Variable Clock Generator Verilog . I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: A clock generator circuit produces a clock signal for synchronising a circuit’s operation. Here is one way to generate the 3 clocks, where the 100mhz clock is synchronous to the other two: Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. // generate 100 hz from 50. In this project we build one using modelsim verilog software. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor part of course).

from www.chegg.com

Here is one way to generate the 3 clocks, where the 100mhz clock is synchronous to the other two: Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. // generate 100 hz from 50. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: A clock generator circuit produces a clock signal for synchronising a circuit’s operation. In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor part of course). In this project we build one using modelsim verilog software.

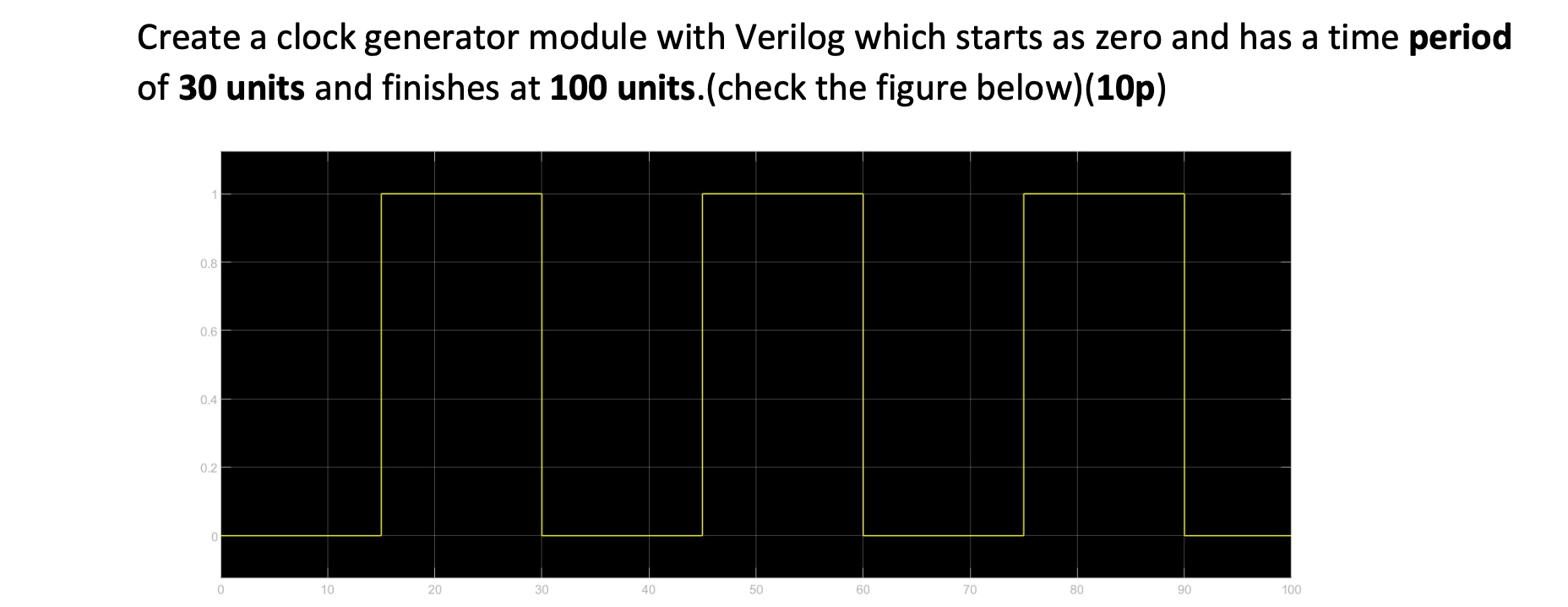

Solved Create a clock generator module with Verilog which

Variable Clock Generator Verilog // generate 100 hz from 50. Here is one way to generate the 3 clocks, where the 100mhz clock is synchronous to the other two: In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor part of course). A clock generator circuit produces a clock signal for synchronising a circuit’s operation. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. // generate 100 hz from 50. Example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. In this project we build one using modelsim verilog software.

From hetpro-store.com

Verilog Diseño de Contadores y Clocks HeTProTutoriales Variable Clock Generator Verilog Here is one way to generate the 3 clocks, where the 100mhz clock is synchronous to the other two: I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. A clock generator circuit produces a clock signal for synchronising a circuit’s operation. I have used following code to. Variable Clock Generator Verilog.

From ramapcsx2.github.io

Si5351 Clock Generator install notes · GBS Control Variable Clock Generator Verilog I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Here is one way to generate the 3 clocks, where the 100mhz clock is synchronous to the other two: Example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: Simulations. Variable Clock Generator Verilog.

From electronica.guru

Cómo crear Verilog o VHDL desde un diseño de Quartus Electronica Variable Clock Generator Verilog In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor part of course). I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. // generate 100 hz from 50. Example verilog code to generate 100 hz from 50 mhz. Variable Clock Generator Verilog.

From www-ug.eecg.toronto.edu

Online Tutorials and Information about peripherials Variable Clock Generator Verilog In this project we build one using modelsim verilog software. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: A clock generator circuit produces a clock signal for synchronising. Variable Clock Generator Verilog.

From www.electronicsforu.com

Software Project Clock Generator Using Verilog Modelsim Variable Clock Generator Verilog I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. // generate 100 hz from 50. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. A clock generator circuit produces a clock signal for synchronising. Variable Clock Generator Verilog.

From www.circuitdiagram.co

Clock Generator Schematic Diagram Circuit Diagram Variable Clock Generator Verilog // generate 100 hz from 50. Example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Here is one way to generate the 3 clocks, where the 100mhz clock is. Variable Clock Generator Verilog.

From www.slideserve.com

PPT Combinational Logic and Verilog PowerPoint Presentation, free Variable Clock Generator Verilog Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. In this project we build one using modelsim verilog software. // generate 100 hz from 50. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Here is one. Variable Clock Generator Verilog.

From www.mdpi.com

Electronics Free FullText A 500 kHz to 150 MHz MultiOutput Clock Variable Clock Generator Verilog I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In this project we build one using modelsim verilog software. // generate 100 hz from 50. A clock generator circuit produces a clock signal for synchronising a circuit’s operation. I have used following code to generate clock (whichever. Variable Clock Generator Verilog.

From www.researchgate.net

Variable frequency clock generator circuit. Download Scientific Diagram Variable Clock Generator Verilog Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. Example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor part of course). I. Variable Clock Generator Verilog.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Variable Clock Generator Verilog I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In this project we build one using modelsim verilog software. In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor part of course). Simulations are required to operate on. Variable Clock Generator Verilog.

From www.electronicsforu.com

Software Project Clock Generator Using Verilog Modelsim Variable Clock Generator Verilog // generate 100 hz from 50. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor part of course). I have used following code to generate clock (whichever value i pass through. Variable Clock Generator Verilog.

From miscircuitos.com

Clock Generator in a FPGA Full code Variable Clock Generator Verilog I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In this project we build one using modelsim verilog software. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Example verilog code to generate 100. Variable Clock Generator Verilog.

From www.vrogue.co

Fpga Based Pwm Signal Generation Digital System Desig vrogue.co Variable Clock Generator Verilog In this project we build one using modelsim verilog software. In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor part of course). I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Example verilog code to generate 100. Variable Clock Generator Verilog.

From miscircuitos.com

Clock Generator in a FPGA Full code Variable Clock Generator Verilog Here is one way to generate the 3 clocks, where the 100mhz clock is synchronous to the other two: // generate 100 hz from 50. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. In one of the exercises, they asked to generate a clock using structural verilog only (except. Variable Clock Generator Verilog.

From lpacademy4students.blogspot.com

Verilog Code for Clock Divided by 3 Variable Clock Generator Verilog I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In this project we build one using modelsim verilog software. Example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: I have used following code to generate clock (whichever value. Variable Clock Generator Verilog.

From www.multisim.com

555 Timer 1hz Multisim Live Variable Clock Generator Verilog I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor. Variable Clock Generator Verilog.

From www.slideserve.com

PPT So you think you want to write Verilog? PowerPoint Presentation Variable Clock Generator Verilog I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In one of the exercises, they asked to generate a clock using structural verilog only (except for the $monitor part of course). // generate 100 hz from 50. Here is one way to generate the 3 clocks, where. Variable Clock Generator Verilog.

From fercow.weebly.com

Clock divider mux verilog fercow Variable Clock Generator Verilog Example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. A clock generator circuit produces a clock signal for synchronising a circuit’s operation. I have used following code to generate clock (whichever value. Variable Clock Generator Verilog.